您目前所在的位置:首页 > 新闻及活动 > 新闻

2018-05-21

干货|微电子器件显微试样制备技术

来源: 作者: 浏览:2809

半导体是电子产品的核心,信息产业的基石

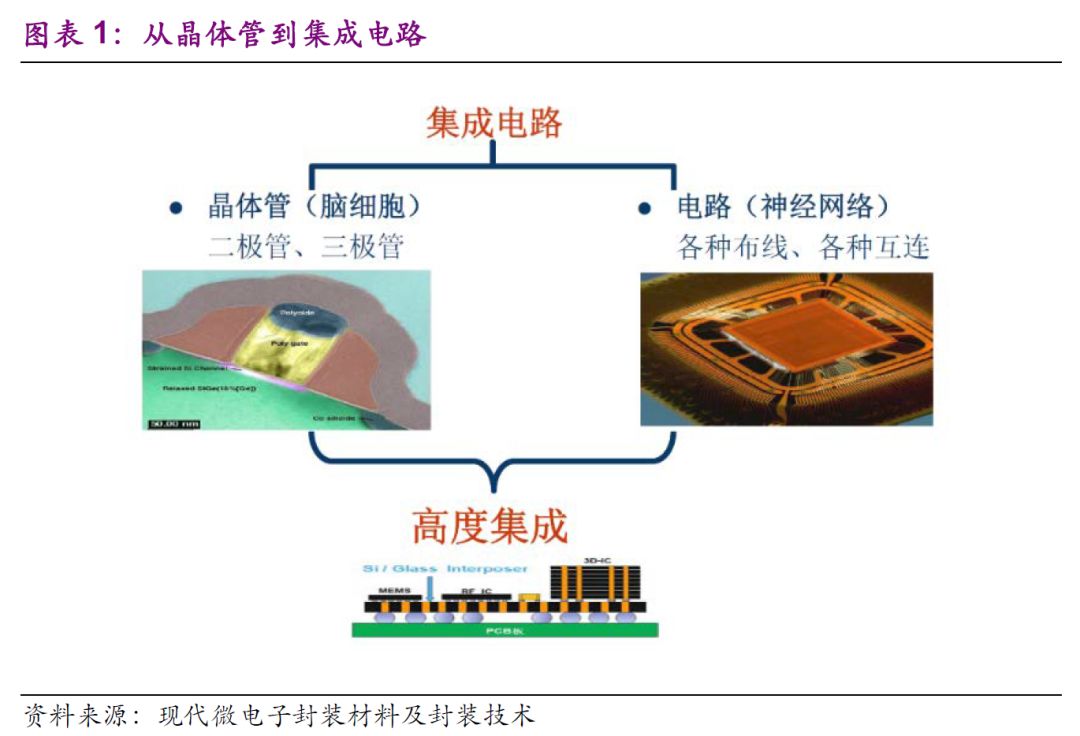

把一个电路中所需的晶体管、电阻、电容和电感等元件及布线互连一起,制作在一小块或几小块半导体晶片或介质基片上,然后封装在一个管壳内,成为具有所需电路功能的微型结构,这便是集成电路,也叫做芯片和IC。集成电路中所有元件在结构上已组成一个整体,使电子元件向着微小型化、低功耗、智能化和高可靠性方面迈进了一大步。

电子产品的核心,信息产业的基石

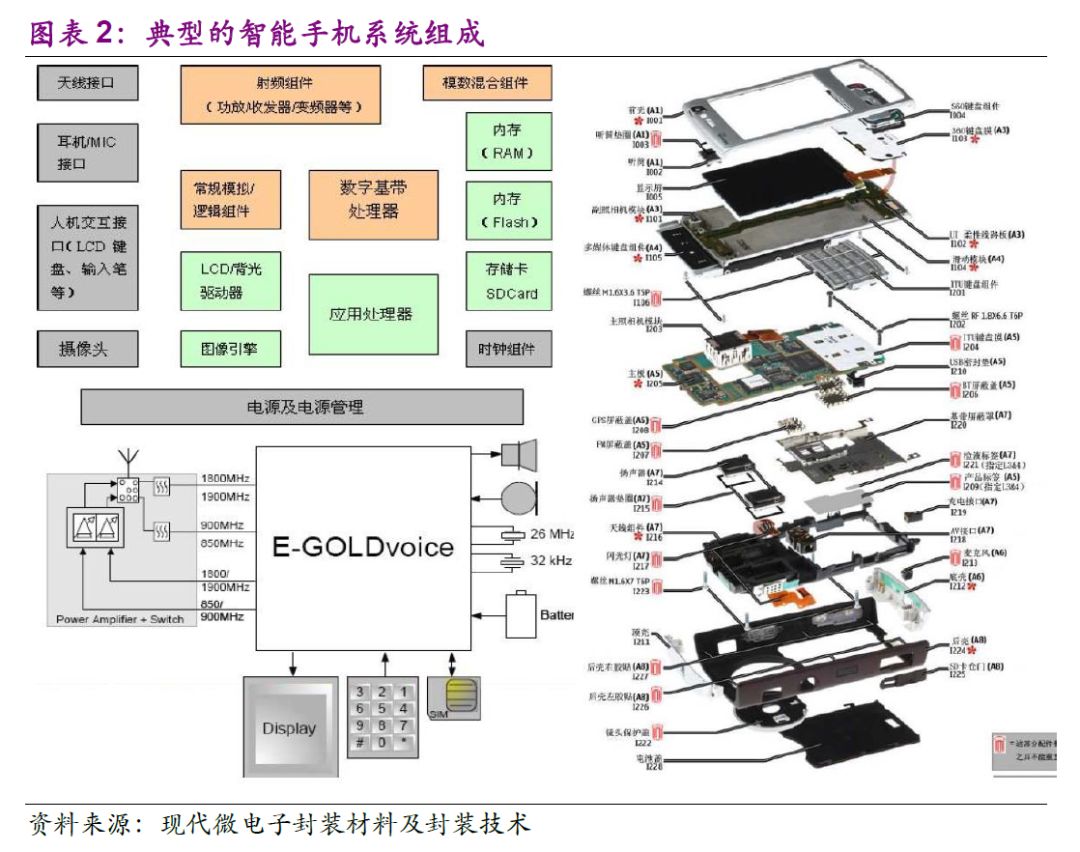

以智能手机为例,诸如骁龙、麒麟、苹果A系列CPU为微元件,手机基带芯片和射频芯片是逻辑IC;通常所说的2G或者4G运行内存RAM为DRAM,16G或者64G存储空间为NANDflash;音视频多媒体芯片为模拟IC。以上这些统统是属于半导体的范畴。

集成电路工序多、种类多、换代快、投资大

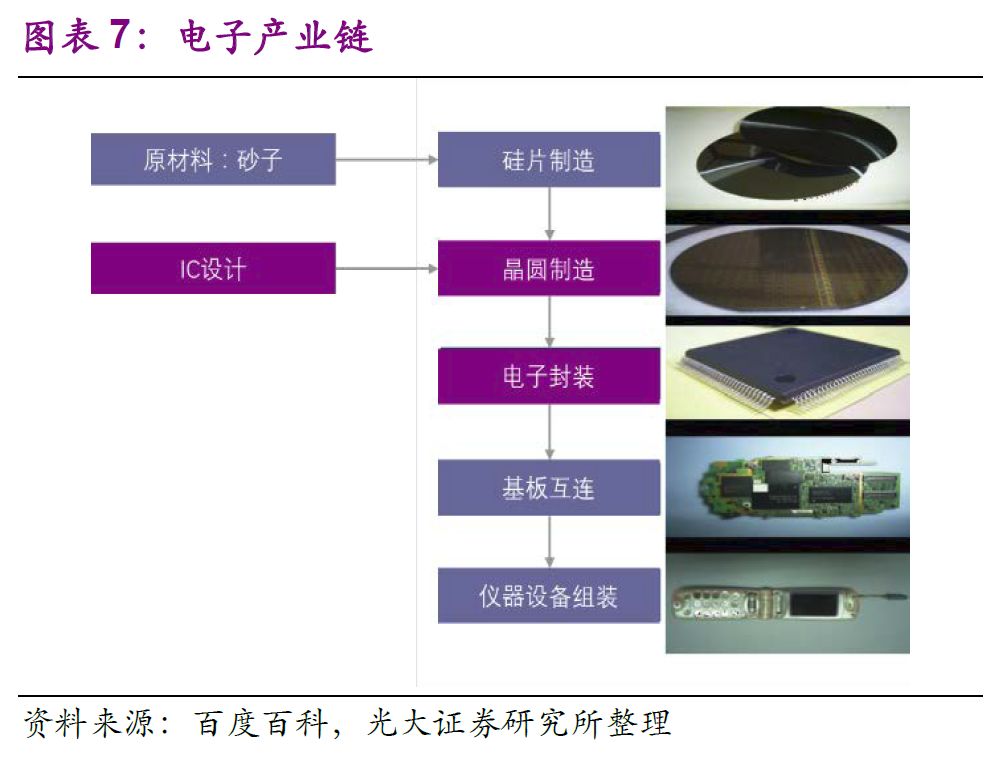

简单的讲,电子制造产业包括:原材料砂子-硅片制造-晶圆制造-封装测试-基板互联-仪器设备组装。集成电路产业链主要为设计、制造、封测以及上游的材料和设备。

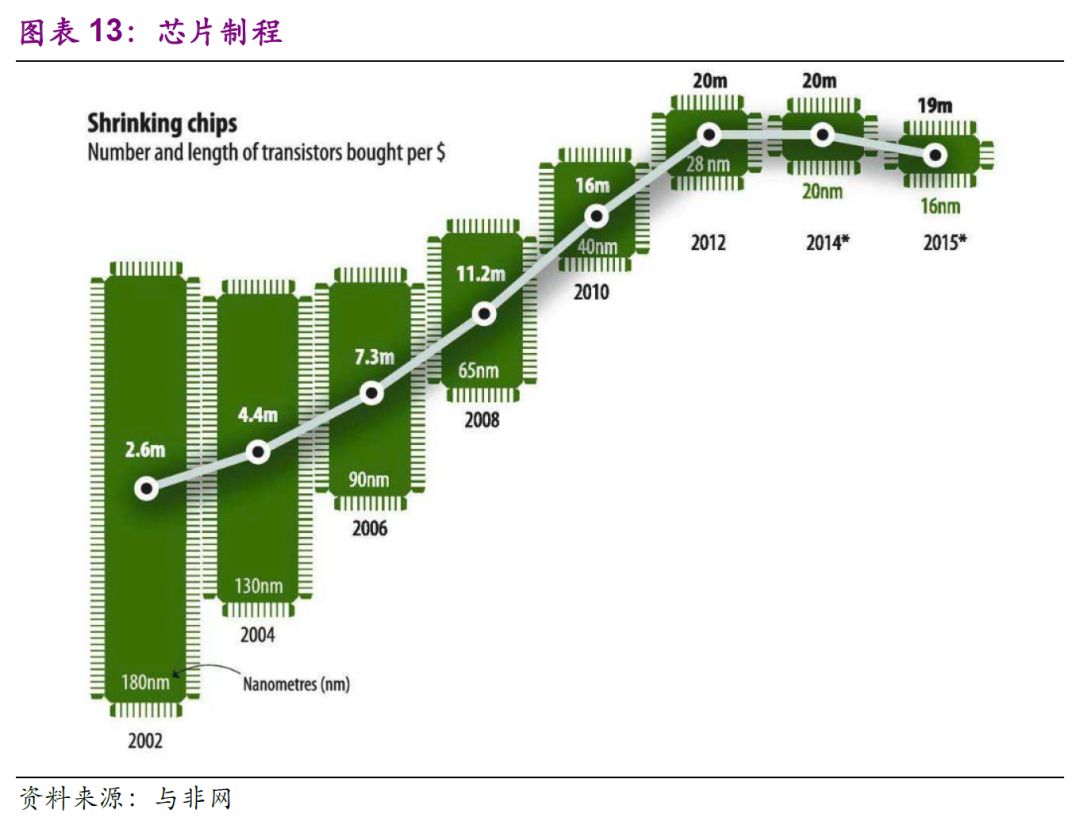

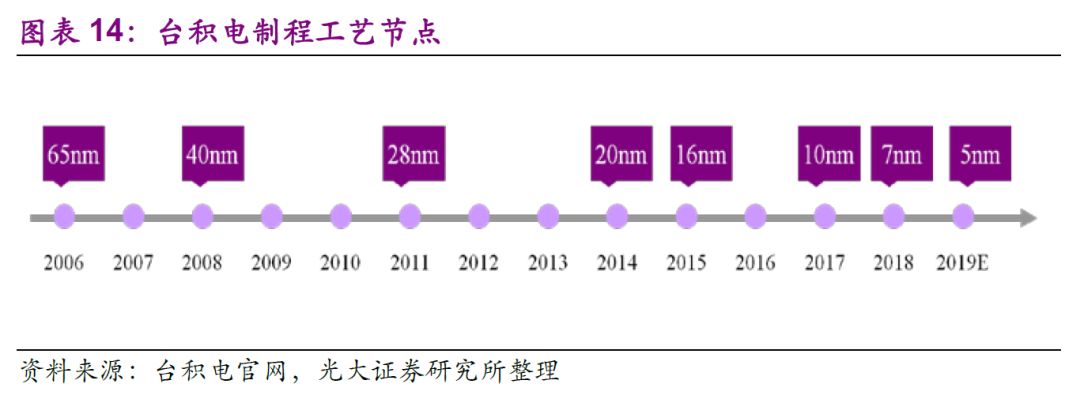

以台积电为例,晶圆制造的制程每隔几年便会更新换代一次。近几年来换代周期缩短,台积电2017年10nm已经量产,7nm将于今年量产。苹果iPhoneX用的便是台积电10nm工艺。除了晶圆制造技术更新换代外,其下游的封测技术也不断随之发展。

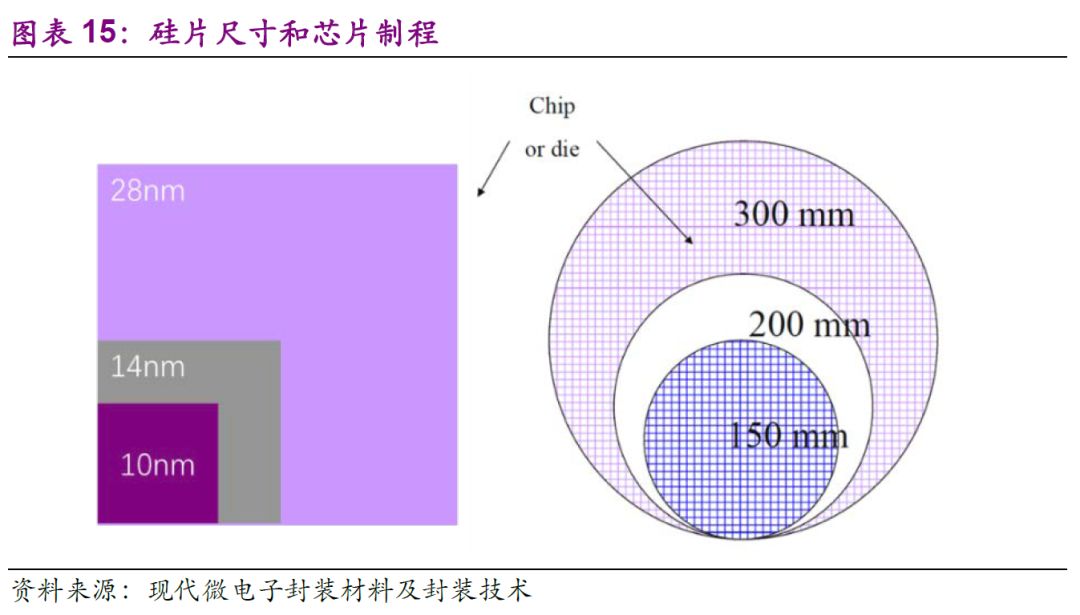

除了制程,建设晶圆制造产线还需要事先确定一个参数,即所需用的硅片尺寸。硅片根据其直径分为6寸(150mm)、8寸(200mm)、12寸(300mm)等类型,目前高端市场12寸为主流,中低端市场则一般采用8寸。晶圆制造产线的制程和硅片尺寸这两个参数一旦确定下来一般无法更改,因为如果要改建,则投资规模相当于新建一条产线。

除了制程,建设晶圆制造产线还需要事先确定一个参数,即所需用的硅片尺寸。硅片根据其直径分为6寸(150mm)、8寸(200mm)、12寸(300mm)等类型,目前高端市场12寸为主流,中低端市场则一般采用8寸。晶圆制造产线的制程和硅片尺寸这两个参数一旦确定下来一般无法更改,因为如果要改建,则投资规模相当于新建一条产线。

集成电路设计存在技术和市场两方面的不确定性。一是流片失败的技术风险,即芯片样品无法通过测试或达不到预期性能。对于产品线尚不丰富的初创设计企业,一颗芯片流片失败就可能导致企业破产。二是市场风险,芯片虽然生产出来,但没有猜对市场需求,销量达不到盈亏平衡点。对于独立的集成电路设计企业而言,市场风险比技术风险更大。对于依托整机系统企业的集成电路设计企业而言,芯片设计的需求相对明确,市场风险相对较小。

现代微电子器件的复杂性

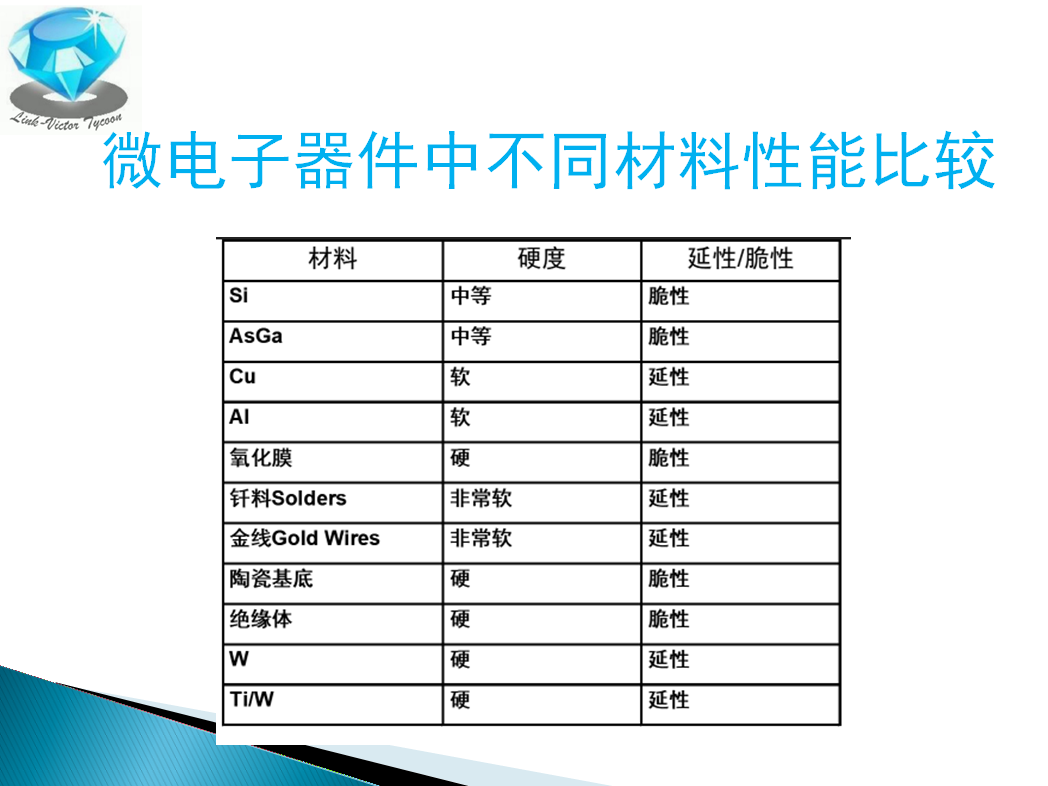

绝大多数微电子器件都是由多种元件组成的复合材料,可以说,微电子材料囊括了范围极为广泛的各种材料,这些材料的力学性能又极不相同。因此,对于这类材料的显微试样,实际上不可能制定出一个能获得理想结果的通用制备方案。

IC封装显微试样切割

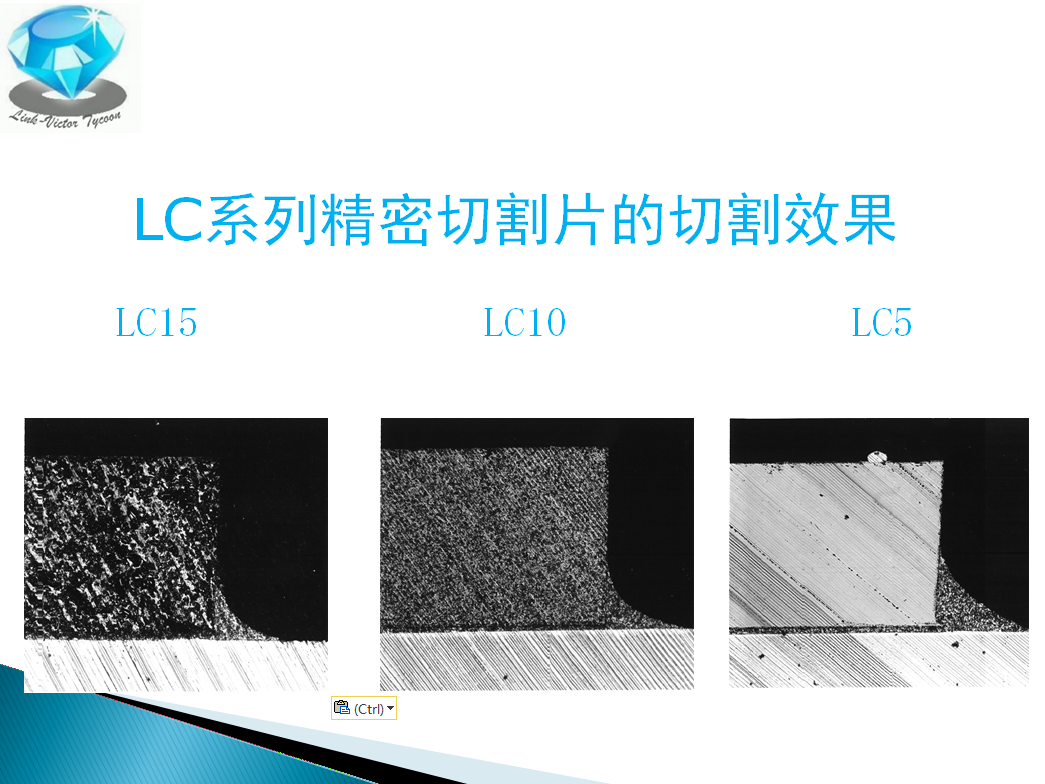

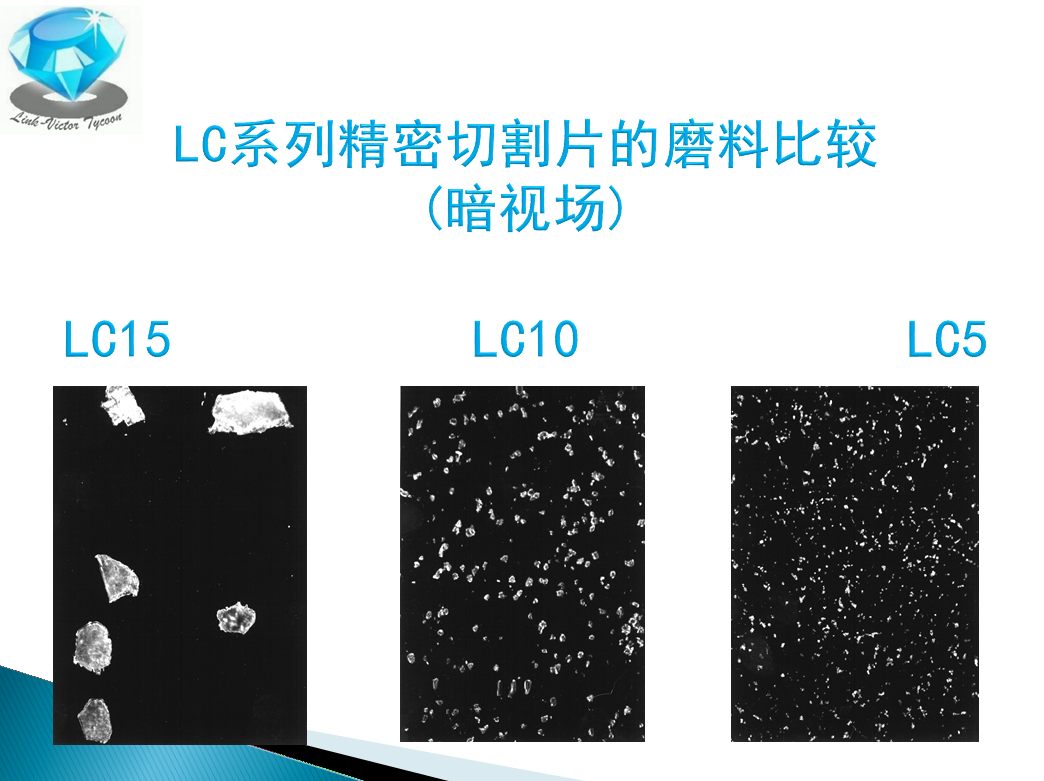

1.为使切割变形损伤减至最小,应使用ISOMET系列低速精密切割机

2.为获得合理的切割速率,使切割片上的金刚石磨料颗粒承受较高的负载,应使用10 LC 低浓度金刚石切割片

IC封装显微试样镶嵌

1.只能使用冷镶嵌

2.冷镶嵌树脂的选用

1)低峰值温度,<90˚C

2)低收缩

3)低粘度

4)透明

5)低磨耗因子(µm/min) EpoThin Epoxicure Epo-Kwick

IC封装显微试样切割后存在的损伤形式:

延性材料—塑性变形,磨痕

脆性材料—脆性破坏,凹坑,裂纹,孔隙

如果磨光时上述缺陷的尺寸越来越小,表明损伤正在逐渐去除;如果缺陷的尺寸在重复同一工序数次后仍无变化,这就意味着损伤层已经去除.。剩下的孔隙就是原始组织的一部分。

IC封装的分类:

厚封装—成型材料的体积分数大于30%

薄封装—成型材料的体积分数小于30%

成型材料(molding compound)的基体为环氧树脂,填料有硬而脆的氧化铝或氧化硅。用SiC砂纸磨光时,使用寿命会相当短,因为破碎的磨料颗粒会进一步在表面造成损伤。

封装试样的磨光:

厚封装与薄封装试样的磨光阶段都是三道工序,厚封装试样使用的制备表面有 Texmet P 和 Texmet; 所用的金刚石磨料粒度分别为15 µm, 9 µm, 和 3 µm.而薄封装试样的前两道工序分别使用 800# 和1200# 的SiC 砂纸,其粒度分别为12 µm 和 7 µm, 只有最后一道工序使用Texmet 和 3 µm 金刚石磨料。

封装试样的抛光

厚封装与薄封装试样的抛光工序使用相同的制备表面和磨料, 即 Mastertex 短绒毛抛光织物和Mastermet 2 悬浮液 (0.02 µm SiO2),抛光液中还可以加入 2% 至 3% 的氨水和过氧化氢,以提高抛光效果。

我们应当把注意力集中在少数几种材料上。首先要考虑的材料就是硅,硅是一种比较硬而脆的材料,不适于用粗碳化硅砂纸进行磨光。否则砂纸上粘接牢固的磨料颗粒会使硅试样的前缘受到很大的冲击损伤,并在硅试样的末缘产生具有破坏性的深裂纹。

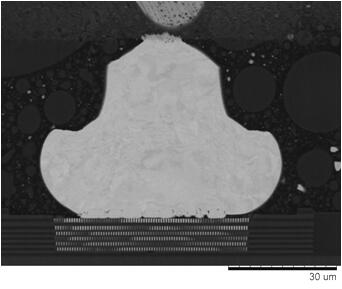

最好采用精密切割,以便尽可能接近目标位置(应使用微电子器件专用切割片), 但是仍需使用细磨料进行磨光,从而能准确地接近目标位置。

因此,硅试样的制备有两类很不相同的方法:

1. 采用传统金相技术;

2. 采用特殊的夹具和磨料制备未经封装的硅晶片

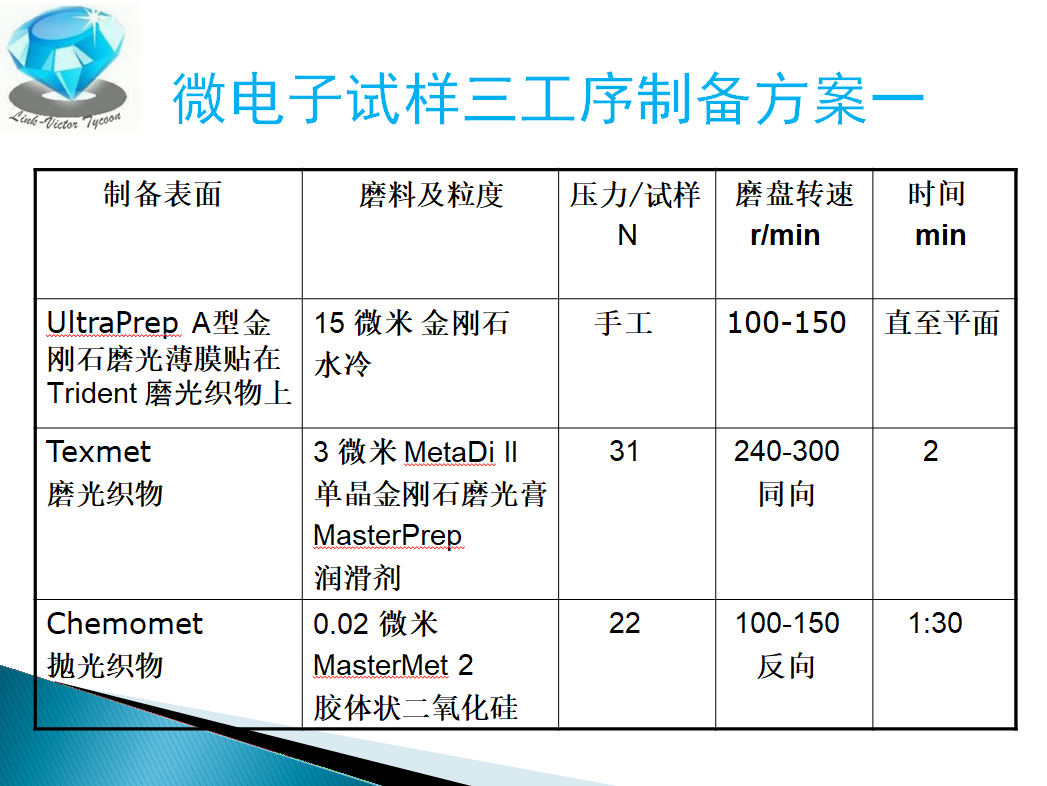

用环氧树脂封装的硅试样的标准制备方法与常用的试样制备方法类似,唯一的例外是只能使用细粒度磨料进行磨光,以下是两个典型的制备方案。

对于微电子器件中的硅晶片部分,胶体状非晶态二氧化硅悬浮液的抛光效果优于氧化铝悬浮液。但是如果需要检验硅晶片与镀镍的铜引线支架连接的部分,则需要用氧化铝悬浮液抛光,以防止镍产生塑性流变,而此时硅晶片部分的抛光效果则属次要。

对于微电子器件中的铝薄膜电路部分, 胶体状非晶态二氧化硅悬浮液的抛光效果很好;但是对于钨和钛-钨及其周围材料,则容易造成难熔金属的表面浮凸和边缘圆角,不利于分析界面组织,解决的办法就是使用粒度极细的金刚石悬浮液进行抛光。

微电子器件封装中的低熔点铅基焊料可分为两类:

1. 焊料为共晶成分或接近共晶成分此时制备方案一仍适用,采用膏状磨料是为了避免磨料和碎屑嵌入延性好的金属,同时应尽量少加润滑剂。

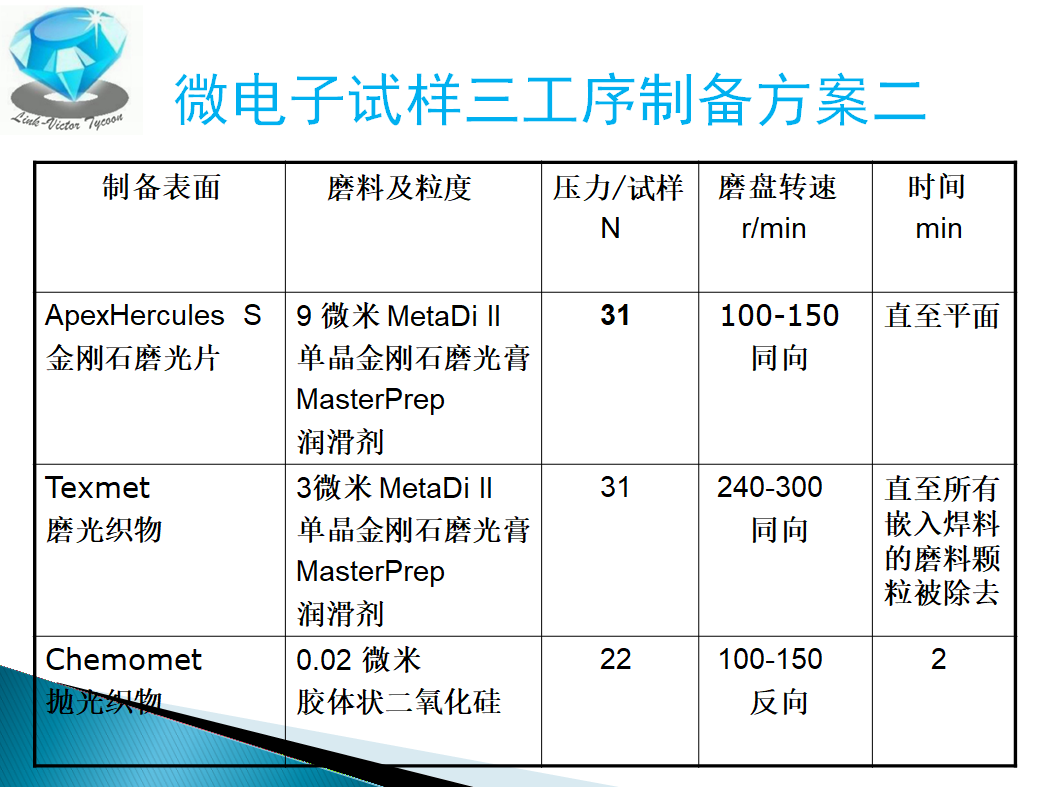

2. 含90-97%Pb的高温焊料这种材料的试样制备比较困难,需要特别予以关注。此时应采用制备方案二。

当器件中包含陶瓷封装时,陶瓷和磨料的碎屑容易嵌入焊料。此时不宜使用碳化硅磨料进行磨光,因为碳化硅的硬度仅仅略高于典型的封装材料,但是却脆得多。

当碳化硅磨料颗粒破碎时,会产生细长的碎屑并深深地嵌入焊料中而不易除去。此外,碳化硅磨料并不能对陶瓷封装进行有效的磨光,从而在与焊料的界面处产生过分的边缘圆角。

金刚石磨料的形状更接近于块状,其优异的材料去除能力可使陶瓷-焊料界面保持平坦.它的碎屑即使嵌入焊料,也更容易被除去。因此,使用金刚石磨光膏在ApexHercules S 磨光盘上磨光时,陶瓷部分可获得良好的制备效果。

与陶瓷连接的高温焊料部分抛光后容易产生不希望有的边缘圆角,但是却无法完全避免。如果使用硬挺的抛光表面,可以减轻上述缺点,但是嵌入焊料的碎屑又会增加。解决的办法就是反复进行磨光-抛光-磨光-抛光,直至获得理想的结果。

两个基本事实

1.不要期望能将一块试样中不同类型材料的所有磨痕全部去除;

2.不要期望能得到一个完美的平坦表面。

电子材料试样制备小窍门

根据最需要检验或观察的部位选用适宜的抛光悬浮液。例如,胶体状二氧化硅悬浮液最适宜用来抛光硅,玻璃,氧化物和铝等.。在一定程度上也可用于铜。但是如果用于镀镍层和金球,则会产生塑性流变。 这时就应使用氧化铝悬浮液,以获得平坦而无划痕的表面。

下一篇:号外|领拓仪器荣获英国Arun代理权